## 学術論文

# 3次元マイクロ波シミュレータ・FDTD メモリマシンの開発に関する研究

### Development of 3D Microwave Simulator by FDTD Memory Machine

川口 秀樹\*2(正員), 高原 健爾\*4 髙﨑 秀樹<sup>\*1</sup>, 松岡 俊佑\*3,

Hideki TAKASAKI, Hideki KAWAGUCHI(Mem.), Shun-suke MATSUOKA, Kenji TAKAHARA

The authors have been working in development of a FDTD dedicated computers for numerical simulation of electromagnetic fields. In the FDTD dedicated computers, there are two kinds of architectures which are oriented for very large scale simulations or high performance computations. In this paper, VHDL cording and FPGA implementation of the large scale simulation type of the FDTD dedicated computer are presented as the final stage of the FDTD machine developments. It is also shown that numerical simulations of microwave phenomena by the FDTD machine has good agreements with that of C language simulations.

Keywords: FDTD, microwave, numerical simulation, FPGA.

## 1 緒言

現在、科学技術計算等において、大規模かつ高速計算 を実現するためにハイパフォーマンスコンピューティン グ(HPC)と呼ばれる技術が活発に研究されており、典型 的には次の3つで代表される形態に分類される。一つは ベクトル処理方式と呼ばれているもので、これは一つの CPU に数百の演算器を装備させ、同時並列処理させる技 術である。ベクトル処理にチューニングしてプログラミ ングすることにより演算器の数だけスケーラブルに並列 化でき、単一演算器の百倍の高性能計算が実現できるが、 基本的に共同利用なので利便性が悪く、また、非常に高 価でもある。二つめはスカラー超並列処理とよばれるも ので、これはネットワークやバス・スイッチに接続され ている多数のコンピュータを並列処理させることにより 高速に大量の処理を実行できるようにする技術である。 この技術は信号解析、暗号解析などデータを独立して扱 える問題に対しては有効であるが、流体や電磁界解析の ような場の解析問題ではコンピュータ間でのデータ通信 が頻繁におこなわれるためそのオーバーヘッドにより効 果的な高速化は困難とされている。そしてもう一つは、 特定の計算目的用に直接ハードウェア化する専用計算機 という技術である。専用計算機は解析対象のスキームに 合わせてアーキテクチャを構成しあらゆるオーバーヘッ ドを最小化するため超高速計算が可能となり、また OS

連絡先: 川口 秀樹, 〒050-8585 室蘭市水元町 27-1,

室蘭工業大字エテロアロン、、こ e-mail: kawa@mmm.muroran-it.ac.jp \*\*\* ロオデジタル研究所 \*\*<sup>2</sup>室蘭工業大学 \*\*<sup>3</sup>旭川工業高 等専門学校 \*4福岡工業大学

の仕様によるメモリ制限がなく必要なだけメモリを搭載 でき大規模計算が可能になるという利点がある。しかし、 その一方で、解析対象に合わせてアーキテクチャを構成 してしまうので、従来の計算機が持つ汎用性という利点 が失われてしまう。

これらの技術の中で、専用計算機は、用途は限られて しまうものの、解析対象に対してはスーパーコンピュー タに匹敵、あるいはそれを上回る性能を極めて安価に実 現できる可能性を秘めており、また、解析対象が十分要 求の高いものであればコストに見合うことも期待できる という観点から、近年さかんに物理学・工学のさまざま な分野で特殊用途に応じ開発が行われている[1-6]。この ような背景のなかで著者らは、これまでマイクロ波・電 磁波にターゲットをしぼったFDTD法専用計算機の開発 をおこなってきた。このときFDTD法専用計算機の構成 では、大規模問題を扱うべくメモリを多く搭載できるよ うにすると計算性能が低くなり、また計算性能を高くし ようとするとメモリ容量に制約がかかるというトレード オフがあり、これらに対応して、大規模計算に特化した FDTDメモリマシン[4,5], および計算性能を重視した FDTDデータフローマシン[6]の 2 つのアーキテクチャを 検討してきた。これまで前者のFDTDメモリマシンの開 発に際しては基本的なアーキテクチャの検討や実現可能 性の検証に主眼をおき、Transistor Transistor Logic (TTL) による試作がおこなわれてきた。これに対して本研究で はさらに実用的なマシンを開発すべく, ハードウェア記 述言語Hardware Description Language (HDL) のうち最近 最もポピュラーとなりつつあるVHDL という言語を用

(49)

いてFDTDメモリマシンの回路設計をおこない, プログラマブルデバイスであるField Programmable Gate Array (FPGA) 上に設計した回路を実装し動作試験をおこなったので報告する。

## 2 ハードウェア用の3次元FDTD法定式化

はじめに本専用計算機で用いるFDTD法の定式化をま とめておく。簡単のため解析領域は真空であるとして, 支配方程式は次のマクスウェル方程式とする。

$$rot\mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t} \tag{1}$$

$$rot\mathbf{B} = \frac{1}{c^2} \frac{\partial \mathbf{E}}{\partial t}$$

(2)

ここで c は真空中の光速をあらわす。

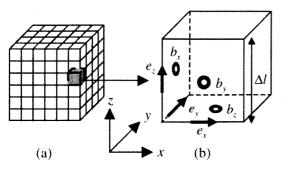

FDTD 法では、空間を Fig.1(a)のような格子状に分割し、これをベースに(1)、(2)を時間領域で差分表現する。簡単な場合として、格子はすべて一様な長さ $\Delta l$ の立方体、時間間隔も全て一様で $\Delta t$ とし、さらに、未知変数を、

$$\mathbf{e} = \frac{\mathbf{E}}{c_0} \tag{3}$$

$$\mathbf{b} = \mathbf{B} \tag{4}$$

と規格化し, クーランの安定条件を

$$\frac{c\Delta t}{\Delta l} = \frac{1}{2} \tag{5}$$

とすると, (1),(2)は

$$\begin{split} &e^n_{x(i+\frac{1}{2},j,k)} = e^{n-1}_{x(i+\frac{1}{2},j,k)} \\ &+ \frac{1}{2} \left[ b^{n-\frac{1}{2}}_{z(i+\frac{1}{2},j+\frac{1}{2},k)} - b^{n-\frac{1}{2}}_{z(i+\frac{1}{2},j-\frac{1}{2},k)} - b^{n-\frac{1}{2}}_{y(i+\frac{1}{2},j,k+\frac{1}{2})} + b^{n-\frac{1}{2}}_{y(i+\frac{1}{2},j,k-\frac{1}{2})} \right] \end{split}$$

$$\begin{split} &e^{n}_{y(i,j+\frac{1}{2}k)} = e^{n-1}_{y(i,j+\frac{1}{2}k)} \\ &+ \frac{1}{2} \left[ b^{n-\frac{1}{2}}_{x(i,j+\frac{1}{2},k+\frac{1}{2})} - b^{n-\frac{1}{2}}_{x(i,j+\frac{1}{2},k-\frac{1}{2})} - b^{n-\frac{1}{2}}_{z(i+\frac{1}{2},j+\frac{1}{2},k)} + b^{n-\frac{1}{2}}_{z(i-\frac{1}{2},j+\frac{1}{2},k)} \right] \end{split}$$

Fig. 1 Per unit grid electromagnetic allocations.

$$e^{n}_{z(i,j,k+\frac{1}{2})} = e^{n-1}_{z(i,j,k+\frac{1}{2})} + \frac{1}{2} \left[ b^{n-\frac{1}{2}}_{y(i+\frac{1}{2},j,k+\frac{1}{2})} - b^{n-\frac{1}{2}}_{y(i-\frac{1}{2},j,k+\frac{1}{2})} - b^{n-\frac{1}{2}}_{x(i,j+\frac{1}{2},k+\frac{1}{2})} + b^{n-\frac{1}{2}}_{x(i,j-\frac{1}{2},k+\frac{1}{2})} \right]$$

$$(8)$$

$$b_{x(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = b_{x(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}}$$

$$-\frac{1}{2} \left[ e_{z(i,j+1,k+\frac{1}{2})}^{n} - e_{z(i,j,k+\frac{1}{2})}^{n} - e_{y(i,j+\frac{1}{2},k+1)}^{n} + e_{y(i,j+\frac{1}{2},k)}^{n} \right]$$

(9)

$$b^{n+\frac{1}{2}}_{y(i+\frac{1}{2}j,k+\frac{1}{2})} = b^{n-\frac{1}{2}}_{y(i+\frac{1}{2}j,k+\frac{1}{2})}$$

$$-\frac{1}{2} \left[ e^{n}_{x(i+\frac{1}{2},j,k+1)} - e^{n}_{x(i+\frac{1}{2},j,k)} - e^{n}_{z(i+1,j,k+\frac{1}{2})} + e^{n}_{z(i,j,k+\frac{1}{2})} \right]$$

(10)

$$b_{x(i+\frac{1}{2},j+\frac{1}{2},k)}^{n+\frac{1}{2}} = b_{x(i+\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}}$$

$$-\frac{1}{2} \left[ e_{y(i+1,j+\frac{1}{2},k)}^{n} - e_{y(i,j+\frac{1}{2},k)}^{n} - e_{x(i+\frac{1}{2},j+1,k)}^{n} + e_{x(i+\frac{1}{2},j,k)}^{n} \right]$$

(11)

と FDTD 法により差分化表現される。ここに、上付の添字 n は時間差分のインデックスを、下付の添字 i, j, k にはそれぞれ x, y, z 方向の差分のインデックスをあらわす。すなわち、これらの式は加減算と 1/2 の乗算のみで構成されており、1/2 は 1 ビット右シフトで実現できるため非常にハードウェア化に適した定式化となる。

## 3 FDTD メモリマシンのハードウェア構成

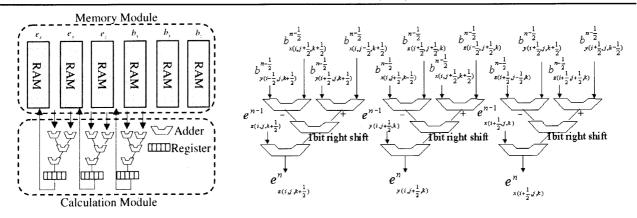

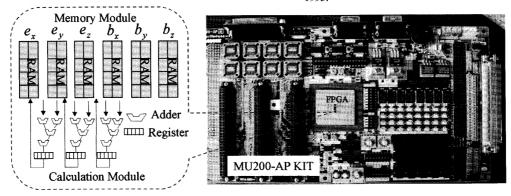

FDTD メモリマシンのハードウェア構成を Fig.2 に示 す。大別して電磁場の各成分の値を格納するメモリモジ ュールと(6)~(11)の FDTD 法のスキームを実行する演算 モジュールの2つのモジュールから構成されている。基 本的な動作は、メモリモジュールから逐次1格子ごとの 値を取り出し、演算モジュールで (6) - (11) の FDTD 法 のスキームに従って場の時間発展の計算をしたあと、再 び計算結果((6)-(11)の右辺)をメモリに戻すというも のである。また、メモリモジュールと演算モジュールは 分離・独立化しているので解析対象がどんなに大規模に なったとしても複雑な回路を有する演算モジュールはそ のままで、メモリモジュールのみを交換することで柔軟 に対応できるようになっている。Fig.3 には演算モジュー ルの詳細を示す。すなわち、演算モジュールでは1グリ ッド分のFDTD法のスキーム (6)~(11) を1クロックで同 時並列計算できるように加減算器とレジスタが x, y, z

(50)

(7)

Fig. 2 Configuration of FDTD memory

の各成分, それぞれ配置されている (Fig.3 は電場を計算しているケース(6)~(8)を示す)。 また, メモリモジュールでは場の各成分を別々のメモリに分割し, それぞれが独立にアクセスできるよう複数のポートが設けてある。

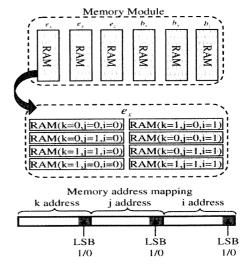

しかし,このとき問題となるのが (6)-(11) にみられる ように、1 つの式の右辺に同じ場の成分が格子のアドレ スを異にして複数現れることである。 すなわち, Fig.2 に 示したようにたとえ場の値を成分ごとに分割してメモリ に格納したとしても、同じ場の成分の異なるアドレスの 値を取り出すには複数回メモリアクセスが生じてしまう。 これでは、Fig.3 のようにいくら演算モジュールを1格子 分の全計算が1クロックで完了するよう設計し計算性能 を向上させたとしても、メモリアクセスにおいて大きく 計算時間をとられてしまう。これに対し、本FDTDメモ リマシンでは、同じ成分のアドレスで隣り合うものだけ が FDTD 法の式に現れるという特徴に着目し、Fig.4 のよ うにi, j, k成分の各最下位ビットが0か1, すなわち場の成分のアドレスが偶数か奇数かで場の各成分ごとのメ モリをさらに分割する方式とした(これにより、場の1 成分だけで8個のメモリに分割される)。このようにする ことで、偶数アドレスと奇数アドレスのメモリに独立に 同時にアクセスできるため (6) - (11) の計算に必要な場 の値は一度に全て演算部にロードでき、メモリアクセス におけるオーバーヘッドを解消することができた。

また、演算モジュール・メモリモジュールの他に FDTD メモリマシンの全体の動作を実現するためには各種制御信号およびメモリを指定するアドレスを生成する回路やパワー入力のための回路が必要となるがこれらは基本的には従来のものと同じ方式を用いた[5,6]。

#### 4 境界条件

FDTD 法を実現するものに (6) - (11) の定式化やパワー入力の他にもう一つ重要なものが境界条件の設定であ

Fig. 3 Configuration of calculation module.

る。実用的に必要な境界条件としては,

- ·完全導体境界条件(金属境界条件)

- 吸収境界条件

- 誘電体境界条件

等があり、これらについてもすでにその具体的な実現方 法の検討はおこなっている[5],[6]。このとき吸収境界条件 に関してはこれまでハードウェアサイズの最小化を考え Mur の 2 次の吸収境界条件を採用していた。しかしなが ら、本FDTD メモリマシンはFPGA により LSI 化するた めこのようなハードウェアサイズの最小化はもはや不要 であるため、本研究ではハードウェアサイズはいくらか 大きくてもより吸収性能のよい PML 吸収境界条件[7]の ハードウェア化の検討をおこなった。PML 吸収境界条件 とは、解析領域の外側に真空の整合条件を満たす吸収媒 質をおくことにより解析領域内への非物理的な反射を回 避する境界条件であり、このような媒質条件を満たすた めにPML媒質内ではマクスウェル方程式を修正した(1) ~(2) とは別の支配方程式が満たされる必要がある。 こ の PML 媒質内での支配方程式対し, (6)-(11) と同様 (3) -(5) を用いて差分化しハードウェア用に定式化すると,

Fig. 4 Improvement of memory module configuration.

(51)

$$e_{xy(i+\frac{1}{2},j,k)}^{n} = A_{y}e_{xy(i+\frac{1}{2},j,k)}^{n-1} + \frac{1}{2}B_{y}\left[b_{z(i+\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}} - b_{z(i+\frac{1}{2},j-\frac{1}{2},k)}^{n-\frac{1}{2}}\right]$$

$$(12)$$

$$e_{xz(i+\frac{1}{2},j,k)}^{n} = A_{z}e_{z(i+\frac{1}{2},j,k)}^{n-1} + \frac{1}{2}B_{z}\left[b_{y(i+\frac{1}{2},j,k-\frac{1}{2})}^{n-\frac{1}{2}} - b_{y(i+\frac{1}{2},j,k+\frac{1}{2})}^{n-\frac{1}{2}}\right]$$

$$(13)$$

$$e_{yz(i,j+\frac{1}{2},k)}^{n} = A_{x}e_{z(i,j+\frac{1}{2},k)}^{n-1} + \frac{1}{2}B_{z}\left[b_{z(i-\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}} - b_{z(i+\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}}\right]$$

$$(14)$$

$$e_{yz(i,j+\frac{1}{2},k)}^{n} = A_{z}e_{z(i,j,k+\frac{1}{2})}^{n-1} + \frac{1}{2}B_{z}\left[b_{x(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} - b_{x(i,j+\frac{1}{2},k-\frac{1}{2})}^{n-\frac{1}{2}}\right]$$

$$(15)$$

$$e_{xz(i,j,k+\frac{1}{2})}^{n} = A_{x}e_{z(i,j,k+\frac{1}{2})}^{n-1} + \frac{1}{2}B_{x}\left[b_{x(i,j-\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} - b_{x(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}}\right]$$

$$e_{yz(i,j,k+\frac{1}{2})}^{n} = A_{y}e_{z(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-1} + \frac{1}{2}B_{y}\left[e_{x(i,j-\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} - b_{x(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{y}b_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{x(i,j,k+\frac{1}{2})}^{n} - e_{z(i,j+1,k+\frac{1}{2})}^{n}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{z}b_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{x(i,j,k+\frac{1}{2})}^{n} - e_{z(i,j,k+\frac{1}{2})}^{n}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{z}b_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{x(i+\frac{1}{2},j,k)}^{n} - e_{z(i,j,k+\frac{1}{2})}^{n}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{z}b_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{x(i+\frac{1}{2},j,k)}^{n} - e_{z(i,j,k+\frac{1}{2})}^{n}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{z}b_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{x(i+\frac{1}{2},j,k)}^{n} - e_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n}\right]$$

$$h_{xy(i,j+\frac{1}{2},k+\frac{1}{2})}^{n+\frac{1}{2}} = A_{z}b_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n-\frac{1}{2}} + \frac{1}{2}B_{z}\left[e_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n} - e_{xi(i,j+\frac{1}{2},k+\frac{1}{2})}^{n}\right]$$

$$h_{x$$

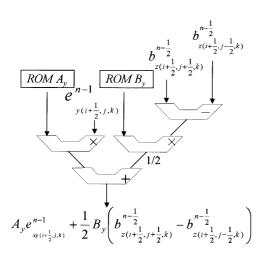

Fig. 5 Configuration of PML ABC calculation module.

$$b_{x(i+\frac{1}{2},j+\frac{1}{2},k)}^{n+\frac{1}{2}} = A_x b_{x(i+\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}} + \frac{1}{2} B_x \left[ e_{y(i,j+\frac{1}{2},k)}^n - e_{y(i+1,j+\frac{1}{2},k)}^n \right]$$

$$b_{y(i+\frac{1}{2},j+\frac{1}{2},k)}^{n+\frac{1}{2}} = A_y b_{y(i+\frac{1}{2},j+\frac{1}{2},k)}^{n-\frac{1}{2}} + \frac{1}{2} B_y \left[ e_{x(i+\frac{1}{2},j+1,k)}^n - e_{x(i+\frac{1}{2},j,k)}^n \right]$$

$$(22)$$

$$A_{l} = \left(1 - \frac{c\Delta t \sigma_{l}}{2} \sqrt{\frac{\mu_{0}}{\varepsilon_{0}}}\right) / \left(1 + \frac{c\Delta t \sigma_{l}}{2} \sqrt{\frac{\mu_{0}}{\varepsilon_{0}}}\right)$$

(24)

$$B_{l} = 1 / \left( 1 + \frac{c\Delta t \sigma_{l}}{2} \sqrt{\frac{\mu_{0}}{\varepsilon_{0}}} \right)$$

(25)

(ただしl=x,y,z,  $\sigma$  は導電率) となる。 (12) - (25) は一見複雑であるが実際には  $A_{l(l=x,y,z)}$  の乗算が加わるのみで真空の(6) - (11) とデータの流れは良く似ておりそこで設計した回路のかなりの部分をそのまま流用できる。(Fig.5)

## 5 VHDL 論理シミュレーション及び FPGA への実装

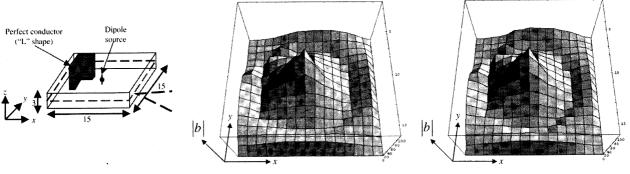

最後に、上記の要領で検討した FDTD メモリマシンを VHDLで設計し論理シミュレーションにより回路をチェ ックした後、実際に FPGA に実装し、動作試験をおこな ったので報告する。今回、動作試験には三菱電機マイコ ン機器ソフトウェア株式会社製の FPGA 評価キット MU200-AP1500 を使用した。(Fig.6)このボードに搭載さ れている FPGA はゲート規模が 150 万ゲート,最大動作 周波数が 40MHz の性能のものである。本研究では、 FDTD メモリマシンの演算モジュール、パワー入力回路 やその他制御信号発生回路、またメモリモジュールすべ てを FPGA 上に実現した。ただし、メモリの容量の制約 で今回は領域外部は完全導体境界とした。シミュレーシ ョンの条件は Fig.7(a) のような解析領域を完全導体境界 条件で囲んだ  $i \times j \times k=15 \times 15 \times 3$  の直方体領域とし、解 析領域の一部に完全導体の散乱体を配置し、中心部(i=8, j=8, k=3)に正弦波源を置いたモデルを想定した。Fig.7(b) には、同マシンでのシミュレーション例として、タイム ステップが 20 のときの k=2 での x-y 平面での磁場の強さ の分布を示す。これは別に同じ条件でC言語でおこなっ たシミュレーション結果(Fig.7(c))とのよい一致が確認で き、FPGA上でFDTDメモリマシンが正常に動作してい ることが確認できた。また、PML 吸収境界条件を含んだ ケースのFDTDメモリマシンは上記の評価キットのメモ リ容量では実現不可能であっため、実マシンでの確認は

できていないが、VHDL 論理シミュレーションは行って おり、ここでも C 言語によるシミュレーション結果との 一致を確認できており、この範囲でハードウェア上で PML 吸収境界条件を含む FDTD メモリマシンが実現可 能であることが確認できている。

#### 6 結言

ハイパフォーマンスコンピューティング技術の1形態 として、マイクロ波シミュレーションにターゲットを絞 った専用計算機・FDTD メモリマシンの方式検討を行っ た。また、VHDLによる回路設計、さらにFPGAへの実 装、動作試験をおこない正常に動作していることを確認 した。以上により、FDTD メモリマシンの基本的な開発 は完了した。今後の課題としては、まず、実用化の最終 段階としてメモリモジュール部分をFPGA キットから独 立させたハードウェア構成の実現があげられる。FPGA の外部にメモリを置く方法としては市販の外部メモリを 装備したFPGA評価キットの使用が考えられるがメモリ を(8分割×6成分)=48分割した本アーキテクチャ はそのようなキットでは不可能であり専用のプリント基 板を製作する必要がある。また、いずれにせよ大規模メ モリを特徴とする本アーキテクチャでは必要なだけメモ リを搭載するには独自にメモリ部を作成する必要がある。 さらにもう一つ, PC とのデータのダウン・アップロード のためのインターフェースの実現も必要と考えられる。 (2005 年 3 月 17 日受付)

#### 参考文献

- [1] J. Makino, GRAPE project: special-purpose computers for many-body simulations, *Comput. Phys. Commun. (Netherlands)*, Vol.139, No.1, pp.45-541, 2001.

- [2] P. Placidi, L. Verducci, G. Matrella, L. Roselli and P. Ciampolini, A custom VLSI architecture for solustion of FDTD equations, *IEICE Trans. Electron.*, Vol.E85-C, No.3, pp.572-577, 2002.

- [3] R. N. Schneider, L. E. Turner and M. M. Okoniewski, Application of FPGA technology to accelerate the finite-difference time-domain (FDTD) method, *Tenth ACM International Symposium on Field-Programmable Gate Arrays*, pp.97-105, 2002.

- [4] H. Kawaguchi, K. Takahara and D. Yamauchi, Design Study of Ultrahigh-Speed Microwave Simulator Engine, *IEEE Trans. Magn.*, Vol.38, No.2, pp.689-692, 2002.

- [5] 川口秀樹,廣瀬公輝,堀田誠人,松岡俊佑,高原健爾,3 次元マイクロ波シミュレータエンジンの基本設計に関す る研究,電気学会論文誌 A, Vol.122, No.12, pp.1038-1044, 2002.

- [6] S. Matsuoka, K. Ohmi and H. Kawaguchi, Study of a Microwave Simulation Dedicated Computer FDTD/FIT Data Flow Machine, *IEICE Trans.*, Vol.E86-C, No.11, pp.2199-2206, 2003.

- [7] A. Taflove and S. C.Hagness, *Computational Electrodynamics:* The Finite-Difference Time-Domain Mathod, Artech House, 1995.

Fig. 6 Configuration of FPGA kit.

(a) Numerical Model

(b) Numerical Simulation by FPGA

(c) Numerical Simulation by C Language

Fig. 7 3D FDTD memory machine operation.